扫描分享

本文共字,预计阅读时间。

摘要

金融量化人才大批涌现、量化选股与多因子策略的国内落地、股指与两融业务相继推出……进入中国才短短十余年的量化投资发展迅速。当前,国内量化体系正处于从低风险量化转向主动量化的行业变革期:大资管行业变革;个股期权、股指期权等金融工具接连推出;交易所技术系统不断升级等。上述变化的发生离不开对应硬件(系统)与软件(人才)的双重升级。硬件方面,拥有更低延时通道、更灵敏的系统响应、更稳定的交易系统是量化策略快速计算、快速运行的必备条件。

由于摩尔定律陷入瓶颈,以及行业日新月异的发展需求,FPGA(Field Programmable Gate Array,即现场可编程门阵列)因其自身独特的可编程、高并行、高带宽等特性优势进入大众视野,并在人工智能、云计算、通信、医疗、航空航天、自动化控制等领域的各应用场景中得到了广泛应用。

金仕达结合国内外金融环境与技术,以基于 FPGA 实现超低延时的沪深 Level 2 行情为切入点,进而深度思考和挖掘 FPGA 在金融交易领域的研究方向。本文通过介绍我司基于FPGA 研发的超低延时行情系统(如FPGA 硬件设计与实现、延时性能等内容),希望有助于交易团队、科技公司等相关方进一步探索FPGA的研究和应用,进而提升交易服务质量、改善投资环境。

一、概述

1.1. 市场的低延时行情需求

作为交易环节的重要组成部分,行情揭示了市场细微实时的变化,更快更精准地获取行情信息则意味着在“起点”快人一步。因此,建设超低延时行情成为提升整体交易速度的必经之路。随着市场基础设施的高速建设与发展,量化交易、算法交易、高频交易等多种自动化投资工具在交易行为中得到了有效的应用。相较于传统的人工盯盘、手动下单交易方式,自动化交易执行拥有更高的处理能力与更快的响应速度,更易在瞬息万变的市场行情中快人一步捕获交易机会并完成交易。在此背景下,低延时的交易数据获取及系统交互广受市场参与者的追捧。低延时通道不仅成为服务商差异化竞争的“法宝”,也成为交易团队在竞争加剧、优胜劣汰的市场中获得更为丰富投资回报的利器。一场围绕构筑超低延时系统的无形军备竞赛正如火如荼地进行。

1.2. FPGA 建设超低延时行情

FPGA(Field Programmable Gate Array,即现场可编程门阵列)是一种可以通过硬件编程语言改变其内部连接结构和逻辑单元,从而可实现自定义功能的芯片,可灵活编程是其与传统 ASIC(专用集成芯片)的显著区别。作为硬件体系结构,FPGA具备硬件的运行速度和可靠性等优势,尤其是在逻辑/算数运算定制、高并行、高带宽等方面表现优异。由 FPGA硬件电路固定延时代替系统软件延时抖动,不仅实现了低延时,同时提高金融交易系统的延时稳定性。

国外对冲基金已将FPGA 硬件加速技术深度植入到交易环节的多个部分。对于国内而言,FPGA 产品在期货行业(如行情、交易柜台、网关风控等多个场景)中的落地为证券行业的低延时建设思路提供了可靠的技术与产品依据。基于在期货行业技术与业务深度积累,我司 FPGA 团队将 FPGA 低延时特性应用在沪深行情的解析中,开发出具有超低延时特性的行情系统。

二、FPGA 硬件行情加速的设计与实现

2.1. 系统整体架构设计及设备选型

FPGA 作为硬件芯片在对数据进行并行计算处理(流水线并行和数据并行)方面具有得天独厚的优势;另一方面,基于 CPU 的软件程序在系统交互实现的便捷性优势亦无需多言。故而,我司采用 “FPGA(RTL)+软件”的异构架构来满足前述的市场需求——通过FPGA 来实现TCP /IP 协议栈,以及以太网MAC 控制器,将原本属于主CPU 的这部分工作由额外的硬件电路完成,从而减轻CPU 的负担,加速网络处理的能力,提升系统的性能。

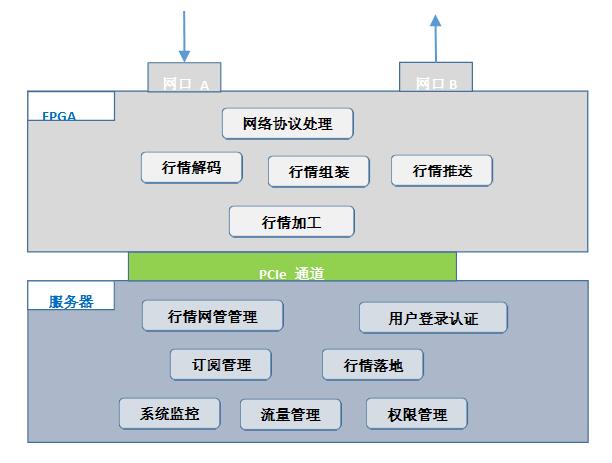

具体而言由 FPGA 硬件部分实现沪深交易所行情数据解析的核心环节,软件部分实现与周边系统交互的管理功能,包括与交易所行情网关(MDGW/VDE)的登录连接管理、行情用户的登录连接管理,以及系统监控等功能。FPGA 板卡与服务器之间通过 PCIe 接口进行数据交互。为实现行情解析全链路低延时的性能方案,我司采用自带网络接口的 FPGA 板卡,在 FPGA 内部完成行情的网络协议解析/重组,实现行情信息解析的端到端收发以及处理。系统整体架构如图1所示。

图 1

基于沪深行情业务,并且考虑到业务的实际应用场景,该FPGA 板卡需要支持如下特性:(1)万兆以太网接口两个及以上,该接口用于接收交易所实时行情源,组播行情推送等功能。(2)PCIe Gen3x8 或 PCIe Gen3x16,并向下兼容 Gen1/2。(3)支持部分可重构(partial configuration),实现热加载硬件 FPGA 版(实现 FPGA版本更新升级与软件版本更新升级相同便捷度)。

2.2. FPGA 硬件行情加速架构

采用自带FPGA芯片的硬件单板,对原始行情数据进行独立的纯硬件解析处理,实现行情接收、行情解码、行情组播等全链路功能。

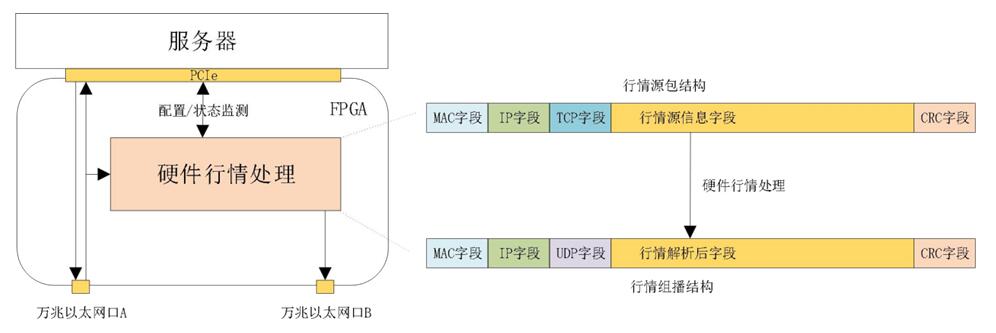

如图2所示,交易所的原始TCP行情数据从万兆以太网口A进入FPGA,通过RTL级设计的行情处理电路在其内部完成行情解析,最终将解码后行情以UDP组播方式以万兆以太网口B发出。

图 2

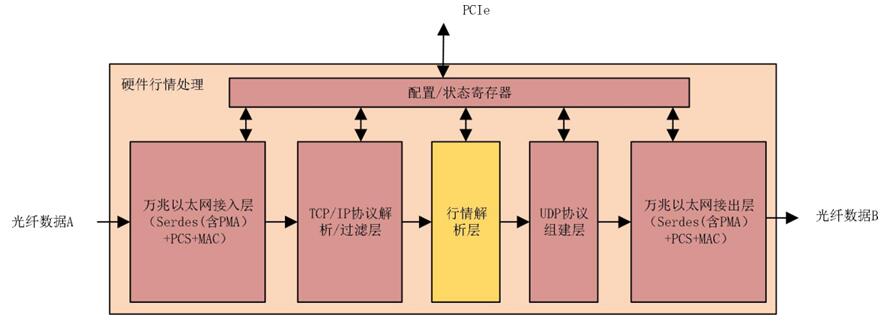

硬件行情处理按处理流程可划分为以下几个部分,如图3所示:

图 3

1. 万兆以太网接入层:实现从光纤上的串行比特数据流中识别出有效数据前导码,将串行数据经过 CRC 校验后,转换成并行数据接口的标准以太网包结构。

2. TCP/IP 协议解析/过滤层:将从万兆以太网接口接收到的包结构按以太网协议格式解析,根据 IP 字段,TCP 字段信息过滤非行情数据包,完成 TCP 保序并提取行情数据包中有效的行情源信息字段,发往行情解析层。

3. 行情解析层:根据交易所(沪、深分别处理)行情传输协议进行解码,解析出所需的各个行情数据字段,发往 UDP 协议组件层。

4. UDP 协议组建层:将解码后的行情数据,按以太网标准协议组建 UDP 组播包,如图3,发往万兆以太网接出层。

5. 万兆以太网接出层:实现与接入层相反的功能,将 UDP 组播包运算出 CRC 字段,并实现将并行包结构数据接口转成串行码流发往光纤。

6. 配置寄存器:该模块通过 PCIe 接口与服务器 HOST 交互。例如:HOST 将行情源的IP/PORT 信息配置到 FPGA 寄存器中,TCP/IP 协议解析/过滤层获取对应寄存器的值,实现对非行情源包的过滤。同时,也会将 UDP 组播包 IP/PORT 信息配置到 FPGA 寄存器中,实现UDP 协议包组建。

7. 状态寄存器:为了实现服务器对FPGA 运行状态监控,各层模块开放一系列内部运行状态寄存器供行情系统软件部分读取,实现行情系统软件部分对硬件监控并做微秒级重启复位等异常后处理。

2.3. 行情协议解析功能实现

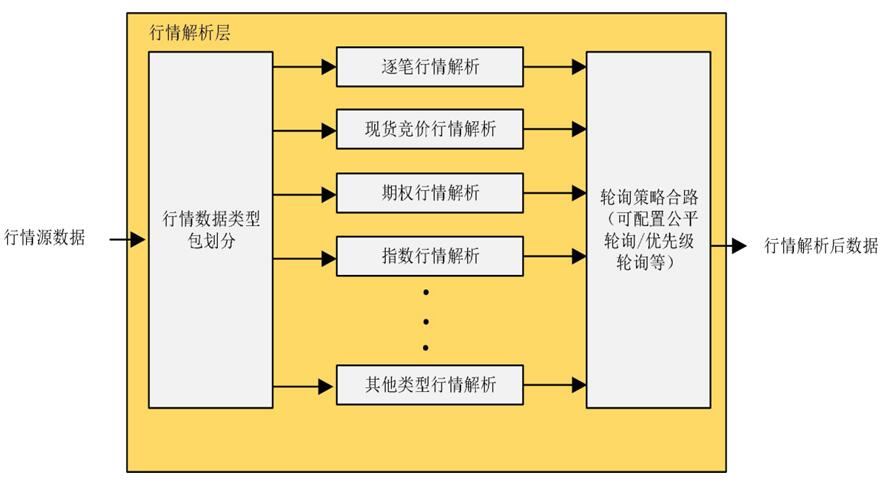

硬件行情加速架构可适用于多种金融应用场景。针对沪深行情而言,行情源中涉及到多种业务(股票/基金/债券/期权/指数等)行情信息。为了实现并行化,提高行情业务数据处理带宽,行情解析层可以采用高并行、业务高扩展结构,如图4 所示(以出口为单个以太网口进行多路轮询合为一路为例)。

图4

同时,针对不同业务的重要性以及速度优先级,可以通过软件灵活置寄存器接口,实现对不同业务数据包的发送优先级。

2.4. 行情性能优化

2.4.1. 数据压缩传输

交易所提供的行情源信息字段中大量数据采用 Unit64 表示,而某些字段实际业务中存在上限值,因此,可以用更短位宽进行表示。例如:交易所规定单笔订单数量最大不超过一百万。数据压缩:(1)可以提高网络报文传输效率,大大减小客户交易端接收行情的延时(通过降低数据长度的方式来调整输出字段格式,将 UDP 发送长度缩减 30%~70%);(2)可以优化数据存储结构,在上交所全量恢复等大量存储访问场景中,减少存储访问次数能够有效地降低快照行情处理延时。

2.4.2. 数据全内部 RAM 存储

行情解析中涉及部分场景需要存储全量或者历史行情信息,如果对位于延时关键路径上的数据处理采用 FPGA 外挂的 DDR 存储器进行存储,其访问周期远大于 FPGA 内部的BLOCK RAM(BRAM)以及分布式 RAM。FPGA 内部的存储器能在单时钟周期完成读写,而DDR 存储器则需要数十个时钟周期延时。在上交所快照全量恢复场景中,延时关键路径上的数据存储采用全 BRAM 的方式,这样可以极大降低快照解析延时。

2.4.3. 多时钟域方案

对于硬件数字电路而言,时钟频率越高,相同电路运算延时越低。在解析字段长度不确定等复杂协议(如上交所 Fast 协议)时,除了在设计解析逻辑时通过提高并行度等方法降低延时以外,还可以对该模块使用更高频率的时钟,使得其运算速率达到最佳,减小关键路径延时。

2.5. 性能验证

2.5.1. 延时性能

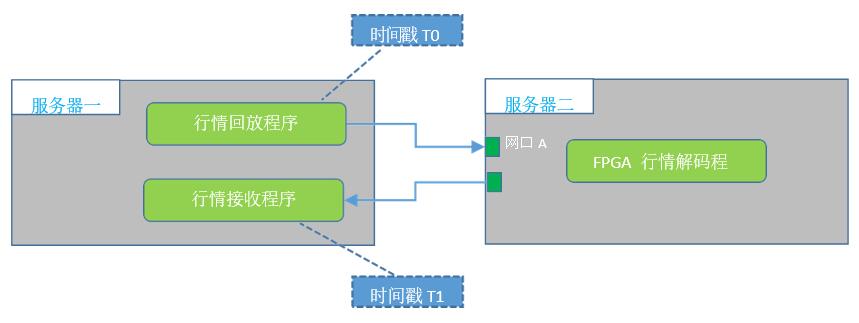

- 验证测试方法

图 5

本延时测试方案是测量从行情源发出时刻 T0 到客户接受到解析后行情时刻 T1 的延时(T0 与 T1在同一台服务器上获取)。鉴于实时行情源(MDGW或 VDE)连接限制的特殊性,故采用行情回放的方式可以有效记录行情源发出时刻 T0,从而进行验证测试。为了有效模拟真实行情系统上下游交互场景,测试需两台服务器,如图 5 所示,服务器二插上FPGA板卡,服务器一通过行情回放程序进行行情播放,原始行情通过光纤进入服务器二上FPAG板卡的万兆以太网口 A,FPGA解析后行情在万兆以太网口 B,通过万兆光纤回传到服务器一的接收网口,行情接收程序接收到该解析后行情,并落地该行情信息以及时间戳 T1。同步,服务器一在发出原始行情时,需要另一种软件行情解析软件程序也对原始行情进行解析处理,以便得到解析后标准行情数据(以便与 FPGA解析后行情进行逐条对应)以及其发送时间 T0,以此用一一对应的方式对硬件解析后行情进行延时测量。

具体步骤测试如下:

Step1——获取回放源:在生产环境中使用网络抓包工具录制一段原始行情数据,即从MDGW/VDE中发出的网络数据包,生成行情 pcap包(TCP协议包)。

Step2——发送行情并获取发送时间:由行情回放程序对 pcap 包进行读取,将该包向网口发出,在发出该TCP包的同时打上时间戳,该时间戳即为该TCP包中所有行情数据的起始时间,记为 T0。

Step3——获取标准数据源:为了对硬件解码行情进行延时测量,行情回放程序同时将对该 pcap源通过另一种软件行情解析程序(位于服务器一上)进行解析,获得逐条解析后行情数据。对每条行情数据对应上发送该TCP包的时间戳 T0。

Step4——获取 FPGA解析后行情,并计算延时:FPGA板卡接收到原始行情TCP协议包进行解析处理,并将解码后的行情数据通过网口 B发往行情接收分析程序。行情接收分析程序在接收到行情数据后逐条记录行情数据到达时间,记为 T1,时间戳使用 clock_gettime 获取,并形成落地文件。行情解析穿透延时即为 T=T1-T0。

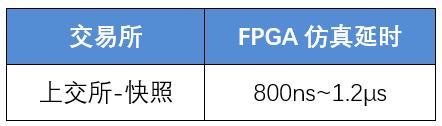

- 测试结果数据

注:因上交所逐笔委托Fast解析累积机制,因包的笔数不同会造成延时数据波动性较大,无法规律统计,这里仅展示快照数据。

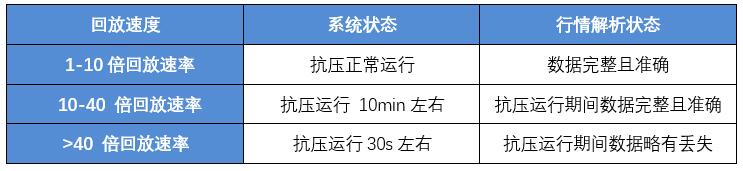

2.5.2吞吐量性能

- 验证测试方法

同延时性能测试方式,通过调整行情回放程序回放速度倍数来实现吞吐量压力测试,测试过程中观察分析行情服务器运行状态以及解析后行情数据,以获取行情服务器的最大吞吐负载。

- 测试结果数据

2.5.3. 数据准确性/完整性

- 验证测试方法

为验证 FPGA行情系统解析数据的正确性以及完整性,将 FPGA 行情系统落地的数据与目前在市面上广泛运用的另一套行情系统解析结果进行对比测试,测试部署方案如图6所示。

图 6

具体测试步骤如下:

Step1——服务器 A、服务器 B 上分别启动 FPGA 行情系统和另一套行情系统,而且两套系统对应的数据接收落地程序、落地格式保持一致。

Step2——行情网关发出的数据通过分光器发往两台服务器,以保证两套行情系统解析的数据源一致。

Step3——编写行情数据对比程序,逐条数据每个数据项一一比对数据正确性,同时判断是否有数据条丢失。输入:两套系统的落地数据,输出:每支股票每条数据的对比结果。

- 测试结果数据

经过长期稳定的测试,根据比对程序输出结果,FPGA 行情系统解析数据稳定无丢失,且数据项均正确。

三、未来FPGA应用展望

FPGA硬件加速技术在交易环节的技术突破需要充分发挥其低延时、高并行、可扩展性、分布式等优点。目前,FPGA 硬件行情产品的商业落地及稳定运行不仅得到了客户的高度认可,同时也为其在证券业务其他场景中的应用潜力提供了有力支持。在此趋势下,金仕达结合市场需求在低延时交易柜台领域进行了尝试与实践,现已实现基于 FPGA 异构的证券低延时交易柜台(柜台稳定穿透延时 3µs)。

未来量化策略的发展将呈现多元化、复杂化,投资者机构化,以及海外机构加速布局。出于对提升市场有效性的迫切需要,大资管行业将加速升级技术系统,FPGA作为低延时赛道的核心技术也因此将成为金融生态系统的关键。鉴于此,金仕达将积极推动高频研究创新中心、仿真态FPGA实验中心、FPGA金融行业云中心的创立,并且将联合知名FPGA厂商及芯片制造商,打造专用高性能硬件设备,为客户提供长期稳定可靠的硬件设施。借助“三中心、一平台”的FPGA金融生态圈,金仕达将在交易合规风控、交易智能执行、量化选股、资讯仓库等多领域进行更深入的探索与尝试,并且期待更多同行加入研发 FPGA行业应用的队伍,加快金融科技的迭代升级,为金融交易能效的提升贡献力量。

(文/上海金仕达软件科技有限公司 FPGA产品经理赵月,上海金仕达软件科技有限公司 FPGA技术专家张强,上海金仕达软件科技有限公司 FPGA高级售前连成浩,上海金仕达软件科技有限公司 公共关系经理赵健榆)

参考来源:

【1】赛灵思(XILINX)公司-

Time is Money: Xilinx and LDA Technologies Set 24.2 Nanosecond Electronic Trading World Record,https://forums.xilinx.com/t5/Xilinx-Xclusive-Blog/Time-is-Money-Xilinx-and-LDA-Technologies-Set-24-2-Nanosecond/ba-p/1112360

【2】Enyx. (2020.6). FPGA for low latency trading: When optimization meets standardization [EB/OL].https://www.enyx.com/blog/fpga-standardization/

【3】Jean Folger. (2019.5). Automated Trading Systems: The Pros and Cons. https://www.investopedia.com/articles/trading/11/automated-trading-systems.asp

【4】Sara Goodman, Rob D’Arco & John Lockwood. (2017.5). The Low Latency FPGA Revolution: The Race To Zero. https://www.rivalsystems.com/news/archive/2017/05/low-latency-fpga-revolution-the-race-to-zero/

非常感谢您的报名,请您扫描下方二维码进入沙龙分享群。

非常感谢您的报名,请您点击下方链接保存课件。

点击下载金融科技大讲堂课件本文系未央网专栏作者发表,属作者个人观点,不代表网站观点,未经许可严禁转载,违者必究!首图来自图虫创意。

本文为作者授权未央网发表,属作者个人观点,不代表网站观点,未经许可严禁转载,违者必究!首图来自图虫创意。

本文版权归原作者所有,如有侵权,请联系删除。首图来自图虫创意。

京公网安备 11010802035947号

京公网安备 11010802035947号